Partners

Consortium

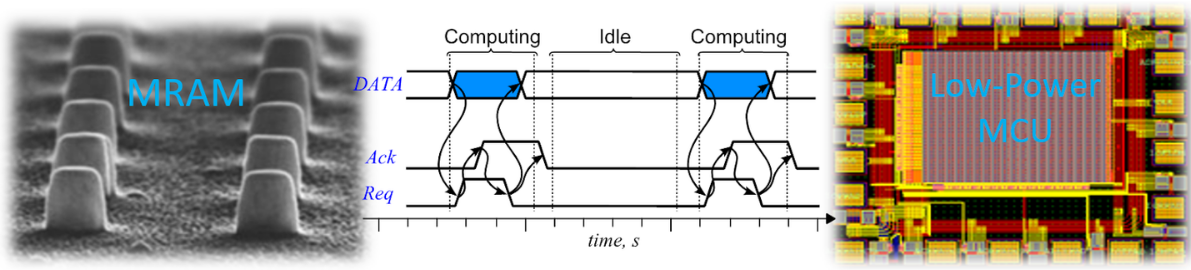

This consortium is complementary according to the scientific responsible of each entity, regarding the selected publications of their biography. SPINTEC has a strong and long experience project coordination such as ANR and European project with 3 FP7/ICT projects already funded. Spintec will manage CAD tool environment and will design and characterize both SOT and peSTT MRAM IPs, CEA-LIST has a strong experience in asynchronous logic design. Apart from participating at ASYNC conferences technical committee for more than a decade, CEA-LIST’s researchers have particularly contributed to the state of the art in Asynchronous Network on Chip (ANoC) and GALS systems (Globally Asynchronous Locally Synchronous), asynchronous implementations of IoT components and also in leveraging the best performances from FDSOI technology process with dynamic body biasing in an asynchronous QDI component. CEA-LIST will develop the digital design part using MTJs, jointly with Spintec. LIRMM, who has been working for many years in high-level simulations of complex digital circuits, will manage the complete system level simulation framework and will be in charge of the deep exploration of multiple configurations. LIRMM will run many simulations for several application benchmarks.

Scientific coordinator: involvement, experience and role in the project

Dr. Gregory DI PENDINA, from Spintec laboratory, will be the coordinator of the project. He is a research engineer in ASIC design, specialized in non-volatile applications based on MRAM technologies. His background comprises full custom and digital design, Hybrid Process Design Kit (H- PDK) development, Design for Testing (DFT), integrated circuit test and characterization. His field of interest is presently mainly focused on “ultra-low power consumption based on MRAM non-volatile synchronous and asynchronous circuits” and “ultra-fast MRAM memory based on Spin Orbit Torque MRAM”. He received his Ph. D in 2012 from the University of Grenoble, France, and his Master degree in 2005 from the University Joseph Fourier of Grenoble, France. He first spent 13 years in a service unit of the CNRS he joined SPINTEC Lab in 2012 as an Engineer - Researcher, involved in several research projects as non-volatile design and test expert and project management. At Spintec he has been leading internal research projects and involved in French ANR research projects, ERC and FP7 European projects as work package leader. He is author or co-author of more than 40 scientific papers and owns 10 patents.

Consortium members

Dr. Pascal BENOIT will act as scientific responsible for LIRMM. He obtained a PhD Degree in Electrical and Computer Engineering from the University of Montpellier, France, in 2004, and then joined the Karlsruhe Institute of Technology in Germany where he has worked as a scientific assistant. Since September 2005, he is Associate Professor at the University of Montpellier. His research activities at LIRMM, Montpellier Laboratory of Informatics, Robotics, and Microelectronics, are focused on the design of secured and energy efficient digital systems. He was the scientific coordinator of the MASTA project (ANR) and is involved in several academic and industrial collaborations (H2020, CIFRE, etc.).

Dr. Jean-Frédéric CHRISTMANN will act as scientific responsible for CEA-LIST. He received the M.S. degree in electronics from the National School of Electronics in 2009 and the Ph.D. degree in micro-electronics and nano-technologies from Grenoble Institute of Technology in 2013. He works as a research engineer in the Digital Design & Architecture Lab since 2009. His research interests include asynchronous design, low power techniques and power management for autonomous Internet-of- Everything systems.